绿能原生自适应电压定位架构 (G-NAVP™) 的 CPU 电源解决方案

摘要

随着中央处理单元(CPU)的发展,其对电源供应的要求也越来越严格。为了满足每一代 CPU 对电源的需求,立锜长期投入于 CPU 电源供应的应用开发,提出了许多全新的电源解决方案。本文介绍一种属于立锜专利的 CPU 电源解决方案,即绿能原生自适应电压定位 (G-NAVP™) 控制架构,该架构具有响应速度快、转换效率高的特色,几乎可满足所有 CPU 电源规格的要求,目前已被业界广泛采用。

1. CPU 电源规格之简介

1.1.微处理器 (中央处理单元: CPU)

微处理器(中央处理单元:CPU)被广泛地使用于许多应用中,如计算机、嵌入式系统和手持装置等。为了不断提升微处理器的性能,往往要将更多的晶体管整合在微处理器里,而随着半导体制造技术的提高,芯片尺寸反而不断降低。自从英特尔 (Intel) 微处理器 4004 在1971年首次发布以来,集成的晶体管数量大致是按照摩尔定律 (Moore’s Law) [1] 不断增长。当英特尔的双核 Itanium 2 处理器于2006年发布时,它的内部已经集成了超过十亿个晶体管,这个数量大约是4004的一百万倍 [2]。2011年,英特尔推出了革命性的、被称为三栅极 (Tri-Gate) 的3-D晶体管设计以提高性能、节省电力 [3],这又是CPU发展过程中的一个里程碑。

CPU性能的充分发挥是高度倚赖于作为平衡输入和功率消耗的电压调节器 (VR) 的。为此,立锜已经提出了数种 VR 控制器以满足每一代CPU的需求。

1.2. 电压调节器 (VR)

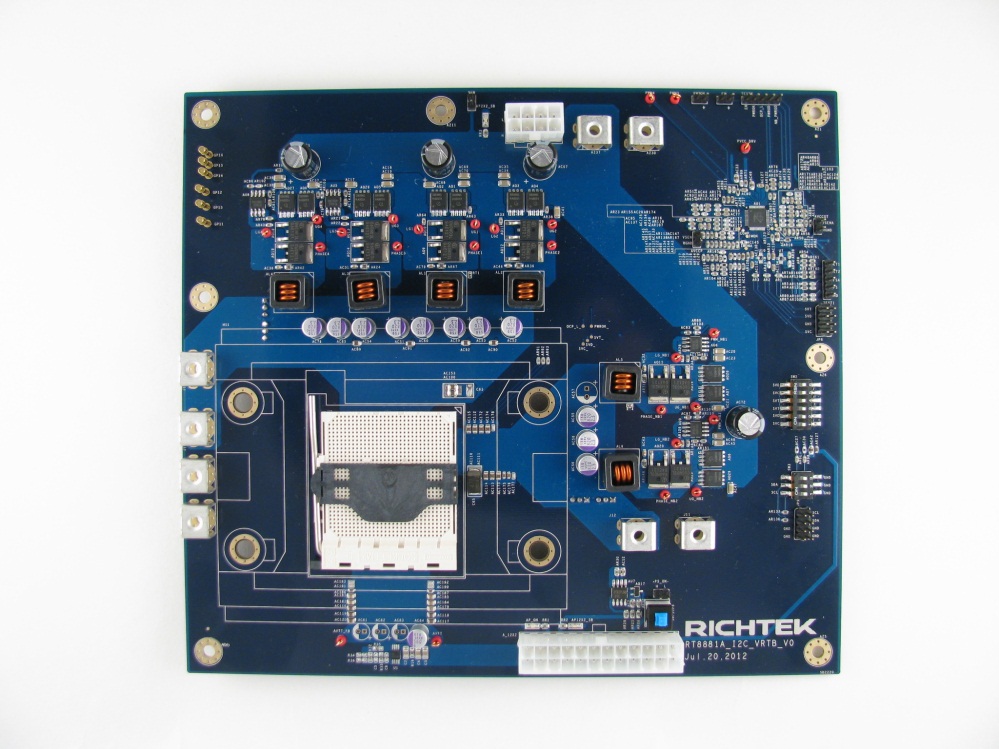

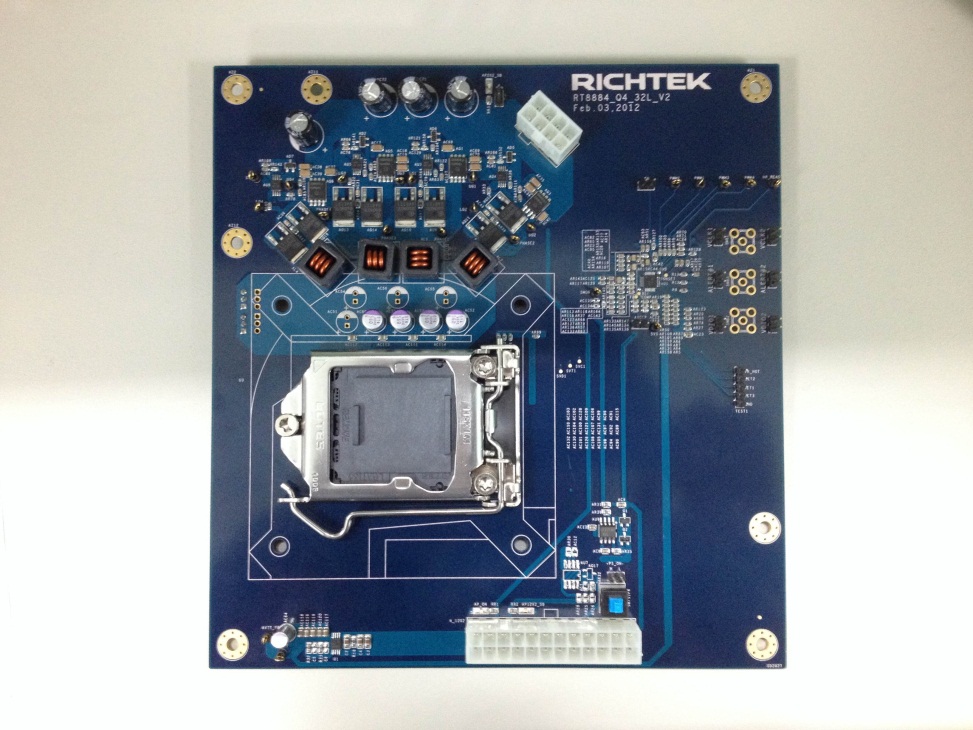

随着微处理器变得越来越强大,其功耗也显著地增加。为了满足微处理器对高电流和低电压的电源需求,业界引入了多相位的电压调节器 (VR)。图一是立锜针对不同CPU的模拟板,图一 (a) 显示的是 AMD SVI2 处理器的CPU电源解决方案,而图一 (b) 显示的是英特尔 VR12.5处理器的CPU电源解决方案。

|

|

|

|

(a)

|

(b)

|

图一、立锜的CPU模拟板。 (a) AMD SVI2 处理器, (b) 英特尔 VR12.5处理器。

一般来说,VR是采用电压模式控制的交插式多相位同步降压转换器。不过,现今VR面临着更严苛的挑战,不仅需要高电流,还有严格的瞬态响应要求。为了使系统能有更快速的响应,并且也为了减少尺寸和成本,立锜提出了 G-NAVP™ 架构的多相位 VR。表一至表四所示为立锜的 VR 控制器与不同 CPU功率规格之间的对应表。

表一、立锜的 VR 控制器,用于 AMD K8/K8_M2 / 英特尔 VR10.x & VR11.x 的CPU电源解决方案

|

控制器型号

|

RT8857A

|

RT8862

|

|

相位数

|

4/3/2/1 相位

|

4/3/2/1 相位

|

|

内建驱动器数量

|

2

|

2

|

|

控制架构

|

电压模式

|

电压模式

|

|

封装

|

WQFN-48L 7x7

|

WQFN-48L 7x7

|

表二、立锜的 VR 控制器,用于英特尔 VR12 的CPU电源解决方案

|

控制器型号

|

RT8859A/M

|

RT8876A

|

|

相位数

|

4/3/2/1 + 1相位

|

3/2/1 + 1相位

|

|

内建驱动器数量

|

0 + 0

|

3 + 0

|

|

控制架构

|

G-NAVP™

|

G-NAVP™

|

|

封装

|

WQFN-56L 7x7

|

WQFN-56L 7x7

|

表三、立锜的 VR 控制器用于英特尔 VR12.5 的CPU电源解决方案

|

控制器型号

|

RT8883A

|

RT8889A

|

RT8884A

|

|

相位数

|

2/1相位

|

3/2/1相位

|

4/3/2/1相位

|

|

内建驱动器数量

|

2

|

3

|

0

|

|

控制架构

|

G-NAVP™

|

G-NAVP™

|

G-NAVP™

|

|

封装

|

WQFN-32L 4x4

|

WQFN-40L 5x5

|

WQFN-32L 4x4

|

表四、立锜的 VR 控制器用于AMD SVI2 的CPU电源解决方案

|

控制器型号

|

RT8877C/D

|

RT8878A/B

|

RT8881A

|

RT8894A

|

|

相位数

|

4/3/2/1 + 2/1/0相位

|

4/3/2/1 + 2/1/0相位

|

4/3/2/1 + 2/1/0相位

|

4/3/2/1 + 2/1/0相位

|

|

内建驱动器数量

|

0 + 0

|

2 + 0

|

2 + 0

|

3 + 0

|

|

I2C 界面

|

N/A

|

N/A

|

支援

|

支援

|

|

控制架构

|

G-NAVP™

|

G-NAVP™

|

G-NAVP™

|

G-NAVP™

|

|

封装

|

WQFN-52L 6x6

|

WQFN-52L 6x6

|

WQFN-52L 6x6

|

WQFN-56L 7x7

|

2. G-NAVP™ 架构之简介

G-NAVP™ 架构是一种具有电流斜坡和AVP功能的纹波型恒定导通时间的控制架构。恒定导通时间控制的特点是在保持重载的高效率时也提高轻载的效率以满足越来越严格的轻载效率规格。增强的轻载效率能提高便携产品的电池使用时间,这对使用者来说是非常重要的特点。AVP功能则是为了节省能源和降低 BOM 成本,而这也是由CPU芯片制造商如英特尔和AMD所规定的功能。

G-NAVP™ 是「绿能原生适应性电压定位」的缩写,这种架构具有许多值得注意的特点:

- 对所有VR之AVP的要求,很容易设定其负载线(下垂)

- 快速的瞬态响应,从而降低了输出电容值和成本

- 轻载时的高效率

- 对所有VR之DC的要求,都有高输出电压准确度

- 对所有VR之纹波的要求,都能使用固定电流纹波

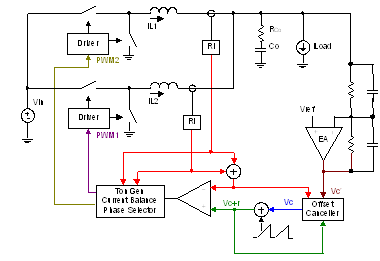

图二为 G-NAVP™ 架构的电路示意图。G-NAVP™ 架构是具有外部斜坡 (ramp) 和DC偏移消除的一种恒定导通时间之电流模式控制。具有有限DC增益的误差放大器 (EA) 可用来调整AVP负载线,并对极点和零点进行补偿。电流信号是透过 DCR 电流检测网络,并用外部斜坡 (ramp) 和 comp信号来调变,其中加上外部斜坡 (ramp) 是为了增加噪声抑制能力。导通时间产生器 (on-time generator) 将随输入和输出电压自动改变导通时间,以使电感器电流纹波在整个输入 / 输出范围内都保持恒定。为能有更精确的输出电压,在回路中加上DC偏移消除功能以消除纹波偏移电压。上述提及的功能不仅增加CPU电源控制器的稳健性和精确度,而且能保有良好的瞬态响应性能。

图二、G-NAVP™ 控制架构之电路图

2.1. 恒定导通时间控制的调变

由于恒定导通时间控制有较快的瞬态响应、良好的轻载效率和更小的组件尺寸,使得它已被广泛采用。对于时下的电池供电产品,较长的使用时间对使用者是很重要的特性之一。因此,恒定导通时间控制所具有的良好的轻载效率能非常好地满足电池供电产品设计者的需求。

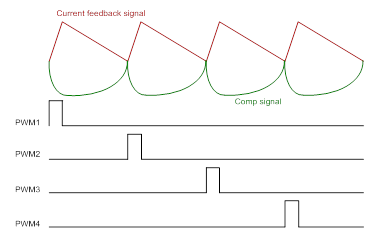

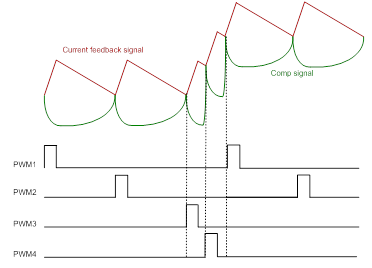

恒定导通时间控制也是一种变频控制。PWM是在连续电流模式(CCM)下,透过电流反馈信号和 comp信号来调变的,如图三所示。当comp 信号上升碰到电流反馈信号时,控制开关打开,经过内部单次触发定时器设定的时间以后才关闭。

图三、在CCM时,基本 G-NAVP™ 调变波形示意图

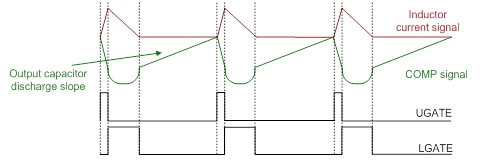

在负载发生瞬态变化的时候,恒定导通时间控制会自动改变开关频率以加快瞬态响应。当负载增大时,关闭时间减少,这相当于提高了开关频率,所以能将更多的能量传送给负载,如图四。当负载下降时,关闭时间增加,相当于降低开关频率,也同时缓和了过冲现象。

图四、在负载上升时,G-NAVP™ 的调变示意图

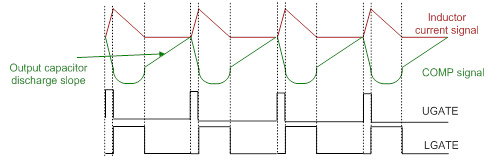

恒定导通时间控制的主要优点是它的轻载效率高。在非连续电流模式(DCM)下,恒定导通时间控制的开关频率与负载电流的大小成正比,如图五所示。轻载时的开关损耗为主要的损耗,所以轻载效率可藉由降低开关频率而得到改善,在图六可以看到在轻载条件下使用恒定导通时间控制可比使用定频控制达到更高的效率。

在 DCM 操作中,低侧MOSFET 如同一个二极管;在电感器电流达到零时,低侧 MOSFET 才会关闭。低侧 MOSFET 被关闭之后,输出电容的放电时间就取决于负载电流。

(a) 负载较轻时,电容放电斜率较图五 (b) 低。

(b) 负载较重时,电容放电斜率较图五 (a) 高。

图五、在 DCM 下,G-NAVP™ 控制的波形示意图:(a) 负载较轻时,(b) 负载较重时。

图六、定频控制与变频控制的效率比较图。

2.2. 固定电流纹波

由于在导通时间内,电感电流纹波正比于输入电压和输出电压之差,电感电流纹波会随输入电压和输出电压而变化,并进一步影响输出电压纹波。

(1)

(1)

固定电流纹波之恒定导通时间(CCRCOT)机制会检测输入和输出电压并自动使导通时间与输入和输出电压之差成反比。以此导通时间控制法,G-NAVP™ 架构可以在宽输入 / 输出操作范围内提供绝佳的输出电压纹波,并能符合输出纹波TOB规格要求,也可以进一步降低输出电容的尺寸。

2.3. 适应性电压定位

目前消费性电子产品的趋势是将产品设计得越来越小,而电源供应器的大小通常须视功率级元件如电感和电容之大小而定。当元件尺寸变小后,散热问题就更为突显。适应性电压定位 (AVP)功能具备节省能源和 BOM 成本的特色,于是为了解决上述问题而被提出。

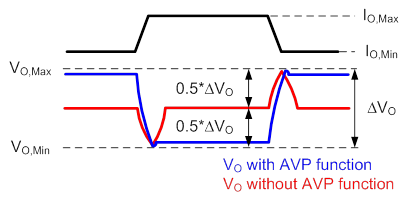

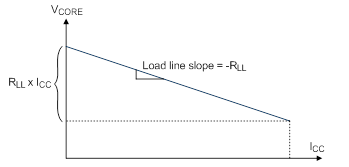

AVP 的基本方法是将输出电压控制在比满载时的最小电压值略高而比轻载时的最大电压值略低的水平上,输出电压容许范围就成了当负载发生瞬态变化时的电压跳升或下降的范围了。图七显示非 AVP 和 AVP 设计之间的瞬态变化的比较图 [4] - [5] 。由于容许电压跳升或下降的幅度变大了,AVP 设计容许使用较少的输出电容,降低 VR 的成本。此外,AVP 控制也使散热设计较为容易,因为在满载时 VR 的输出功率已降低了。

要实现 AVP 功能时,必须将 VR 输出阻抗设计为恒定的,如图八所示。

图七、AVP 的功能示意图

图八、负载电流与输出电压的关系

G-NAVP™ 架构不采用较复杂的类型三 (type-3) 补偿器,反而采用低增益的补偿器(有一个极点和一个零点),且借着低增益补偿中原生的稳态误差来实现 AVP 功能,此架构也因此被称为原生适应性电压定位(NAVP)控制架构。

在G-NAVP™ 架构中,AVP功能的运作需设定经电流回路和电压回路之负载线(下垂)。为使用户能方便使用,立锜在这些 IC 的规格书中都提供了相对应的简要负载线设定公式。

2.4. 斜坡补偿

G-NAVP™ 架构因考虑到噪声边限和抖动,所以采用了斜坡补偿,以增加在开关节点的噪声抑制能力 (noise immunity) 并减少抖动 (jitter) 。此外,藉适当的设计,斜坡补偿也可使模式的切换较为平顺。图九显示有和无斜坡补偿的噪声边限之比较。

图九、有和无斜坡补偿的噪声边限之比较。

3. 结论

随着移动产品市场的增长,电池有限的使用时间和散热等因素使电源效率问题愈来愈被重视,立锜所提供的G-NAVP™ 架构则能兼顾性能和效率的要求,非常符合消费者的需要。

G-NAVP™ 架构采用的是有电流斜坡和AVP功能的固定电流纹波型恒定导通时间控制法。恒定导通时间控制具有快速响应和高效率的特点,AVP 能节省 BOM 的成本,偏移消除电路和斜坡补偿则能提高DC的精确度和噪声抑制能力。结合上述功能,以 G-NAVP™ 为控制架构的VR控制器能提供绝佳的性能,且可满足大多数英特尔和AMD 之 VR 电源规格。

4. 参考数据

|

[1]

|

Intel document, “Moore’s Law Timeline,” Available at http://download.intel.com/pressroom/kits/events/moores_law_40th/MLTimeline.pdf

|

|

[2]

|

Intel document, “Intel Processor History,” Available at http://download.intel.com/pressroom/kits/IntelProcessorHistory.pdf

|

|

[3]

|

Intel document, “Intel®’s 22nm Technologys Moves Transistor Into the 3rd Dimension,” Available at http://www.intel.com/content/dam/www/public/us/en/documents/backgrounders/standards-22-nanometers-technology-backgrounder.pdf

|

|

[4]

|

Kaiwei Yao, Yuancheng Ren, Julu Sun, Kisun Lee, Ming Xu, Jinghai Zhou and Fred C. Lee, “Adaptive Voltage Position Design for Voltage Regulators,” IEEE APEC’04.

|

|

[5]

|

Jian Rong Huang, Sophia Chien-Hui Wang, Chia Jung Lee, Eddie Kuo-Lung Tseng and Dan Chen, “Native AVP Control Method for Constant Output Impedance of DC Power Converters,” IEEE PESC’07.

|